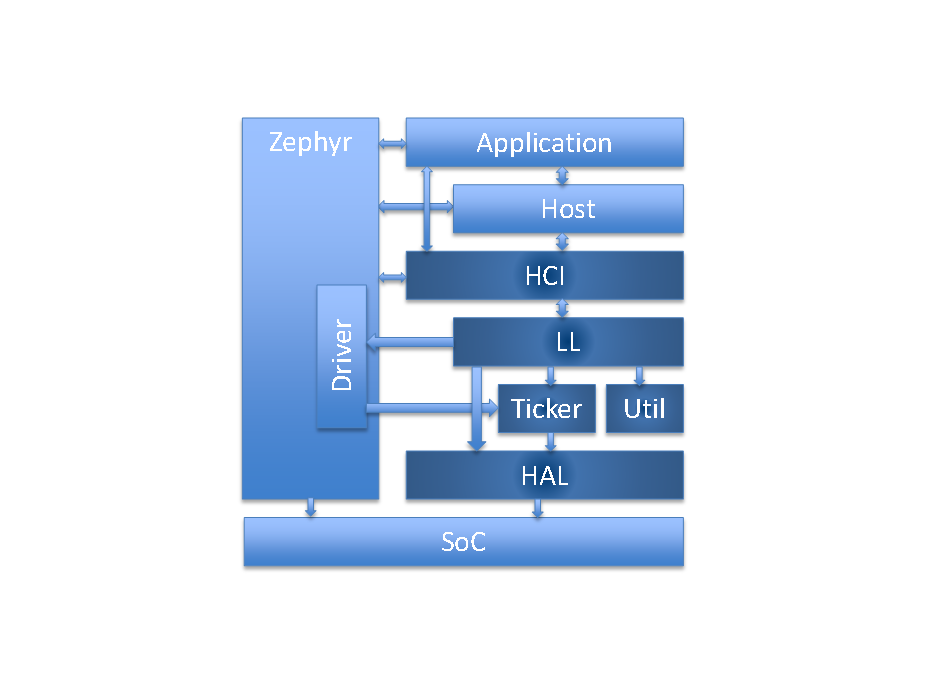

LE Controller

Overview

HCI

Host Controller Interface, Bluetooth standard

Provides Zephyr Bluetooth HCI Driver

HAL

Hardware Abstraction Layer

Vendor Specific, and Zephyr Driver usage

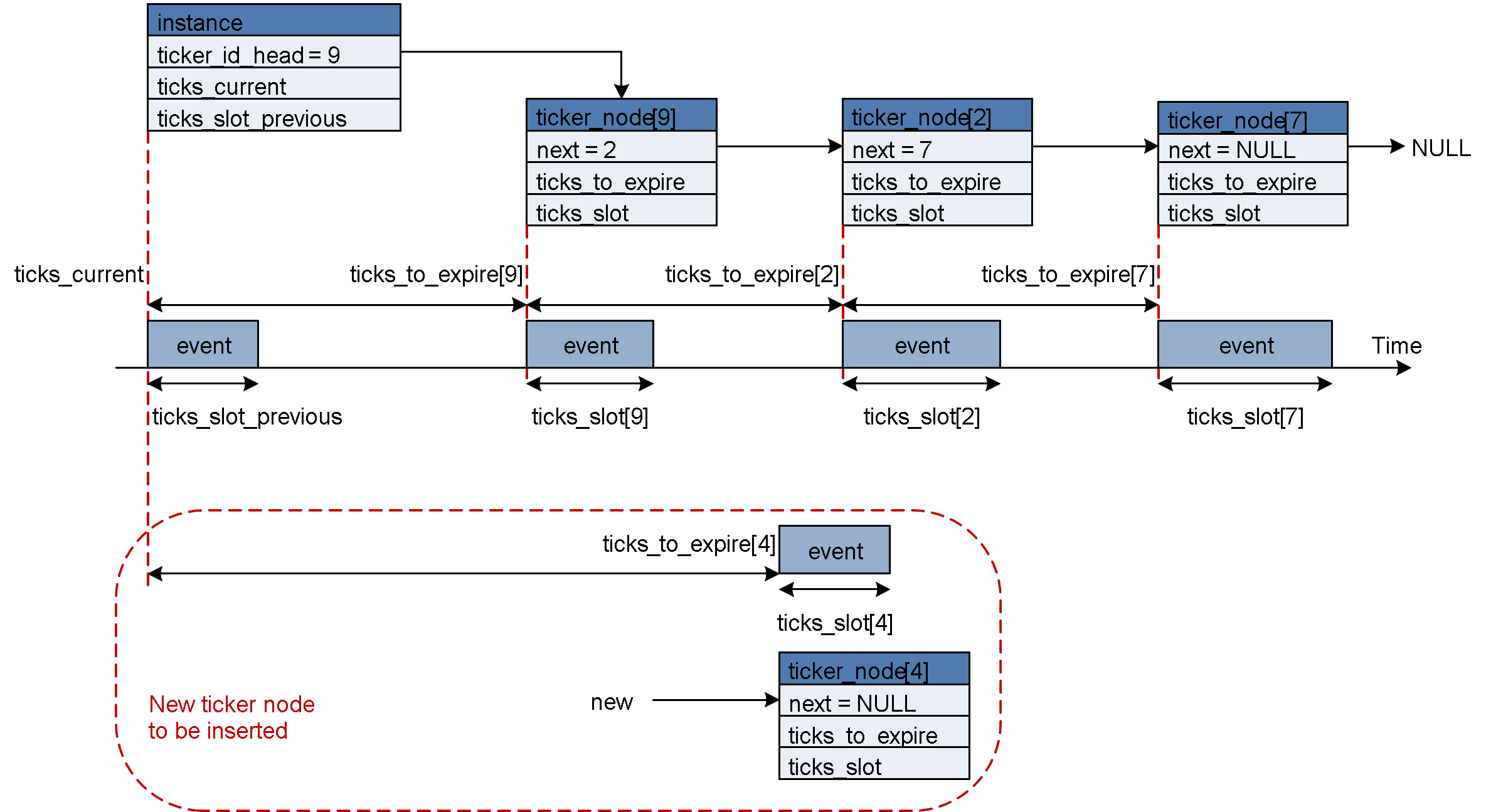

Ticker

Soft real time radio/resource scheduling

LL_SW

Software-based Link Layer implementation

States and roles, control procedures, packet controller

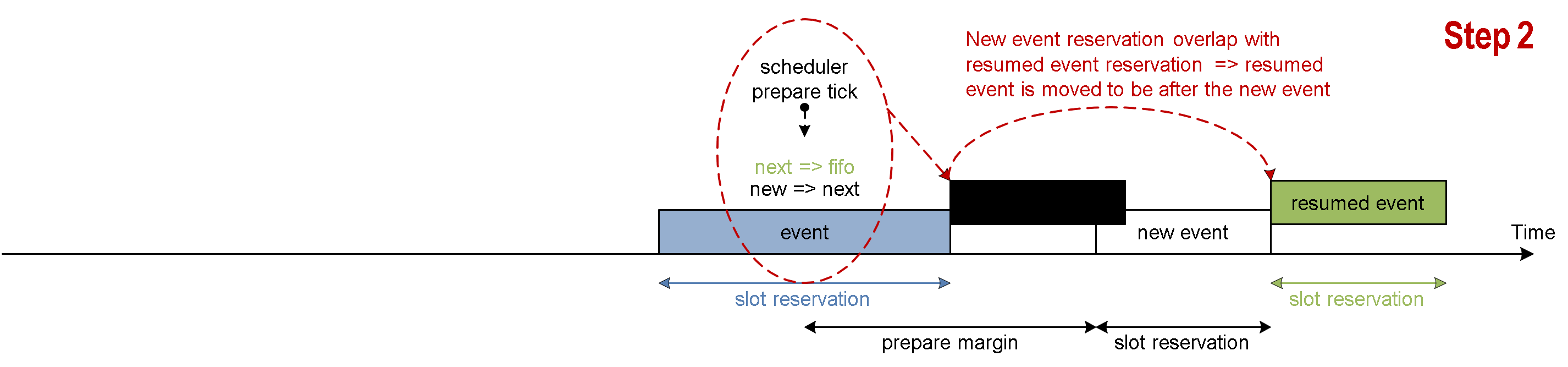

Util

Bare metal memory pool management

Queues of variable count, lockless usage

FIFO of fixed count, lockless usage

Mayfly concept based deferred ISR executions

Architecture

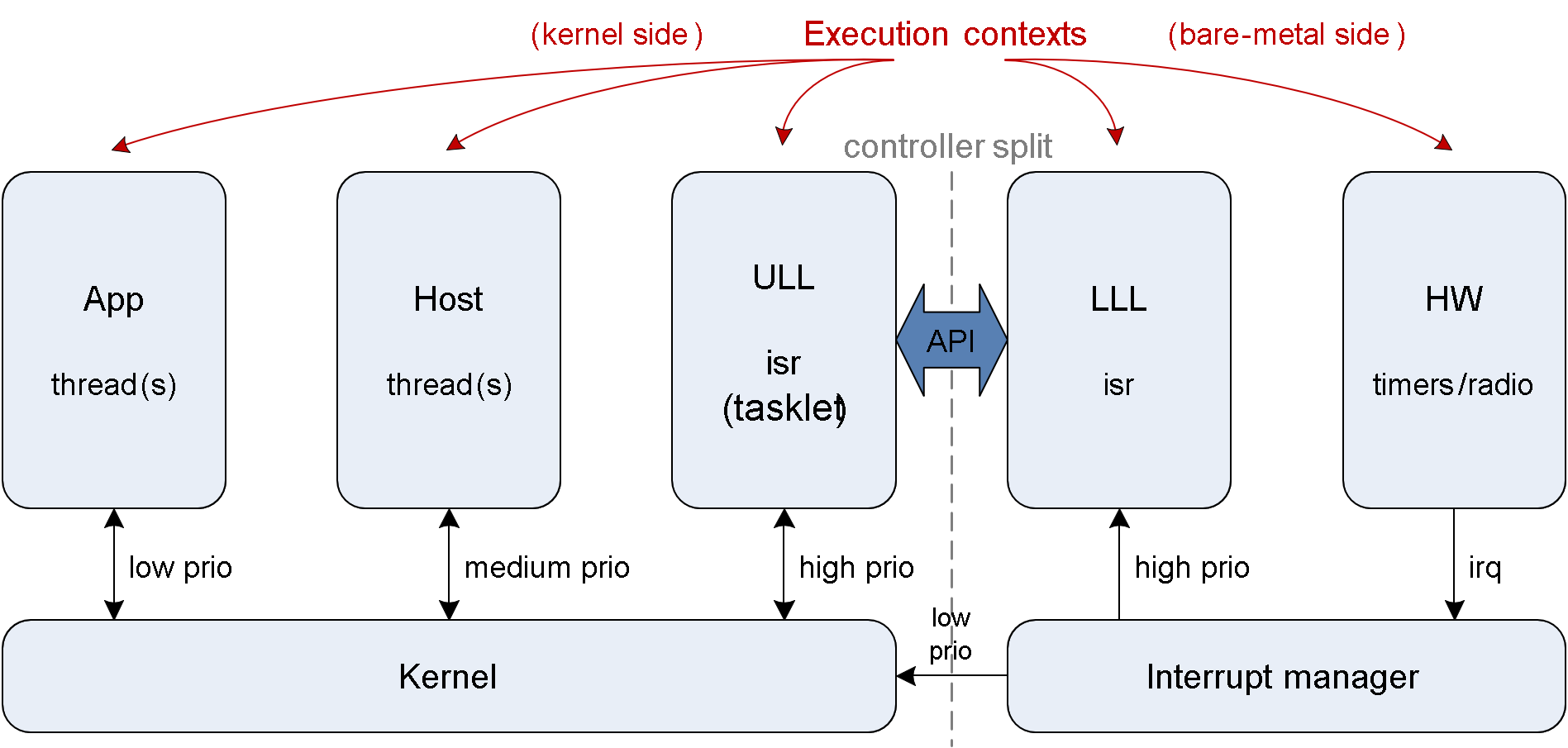

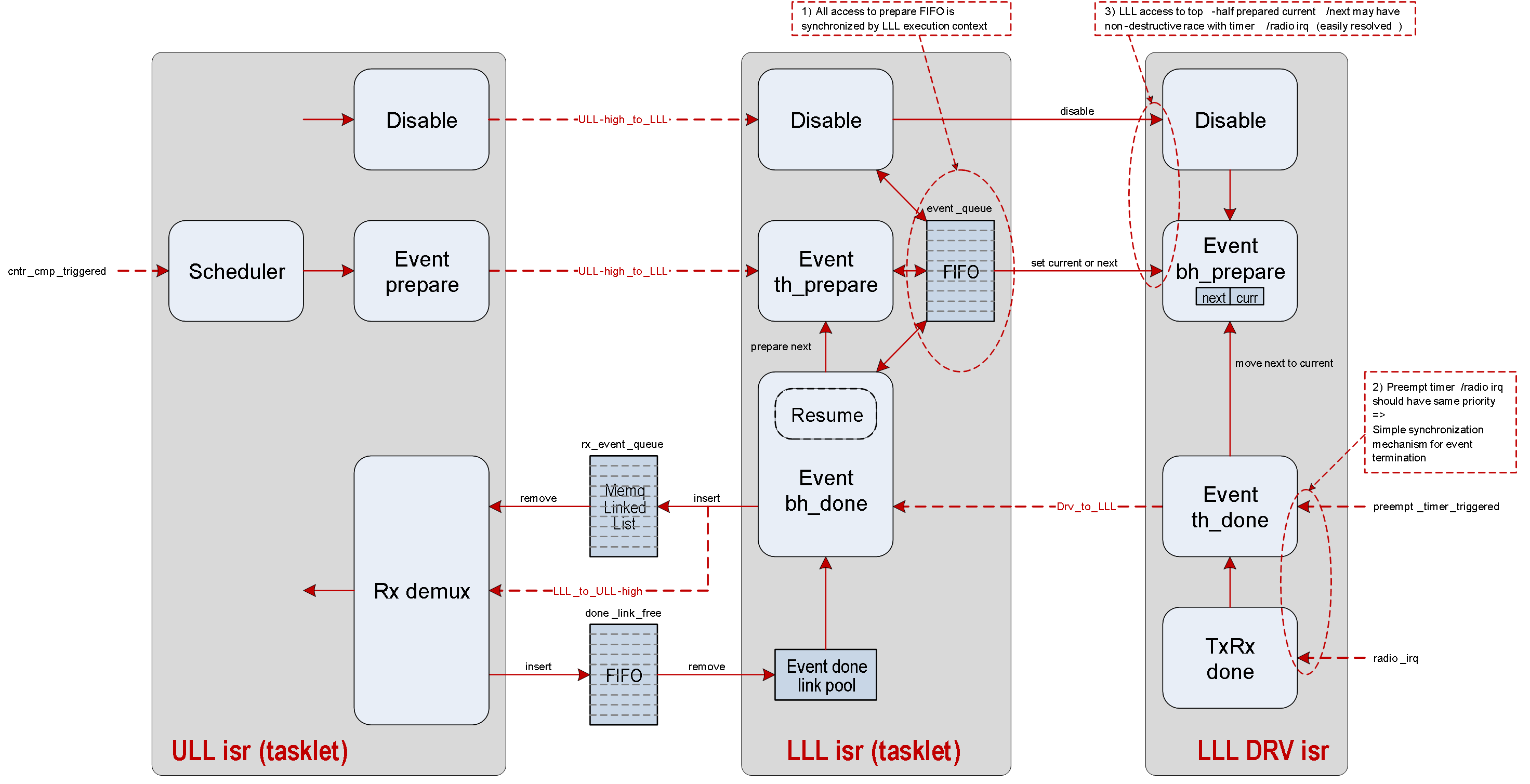

Execution Overview

Architecture Overview

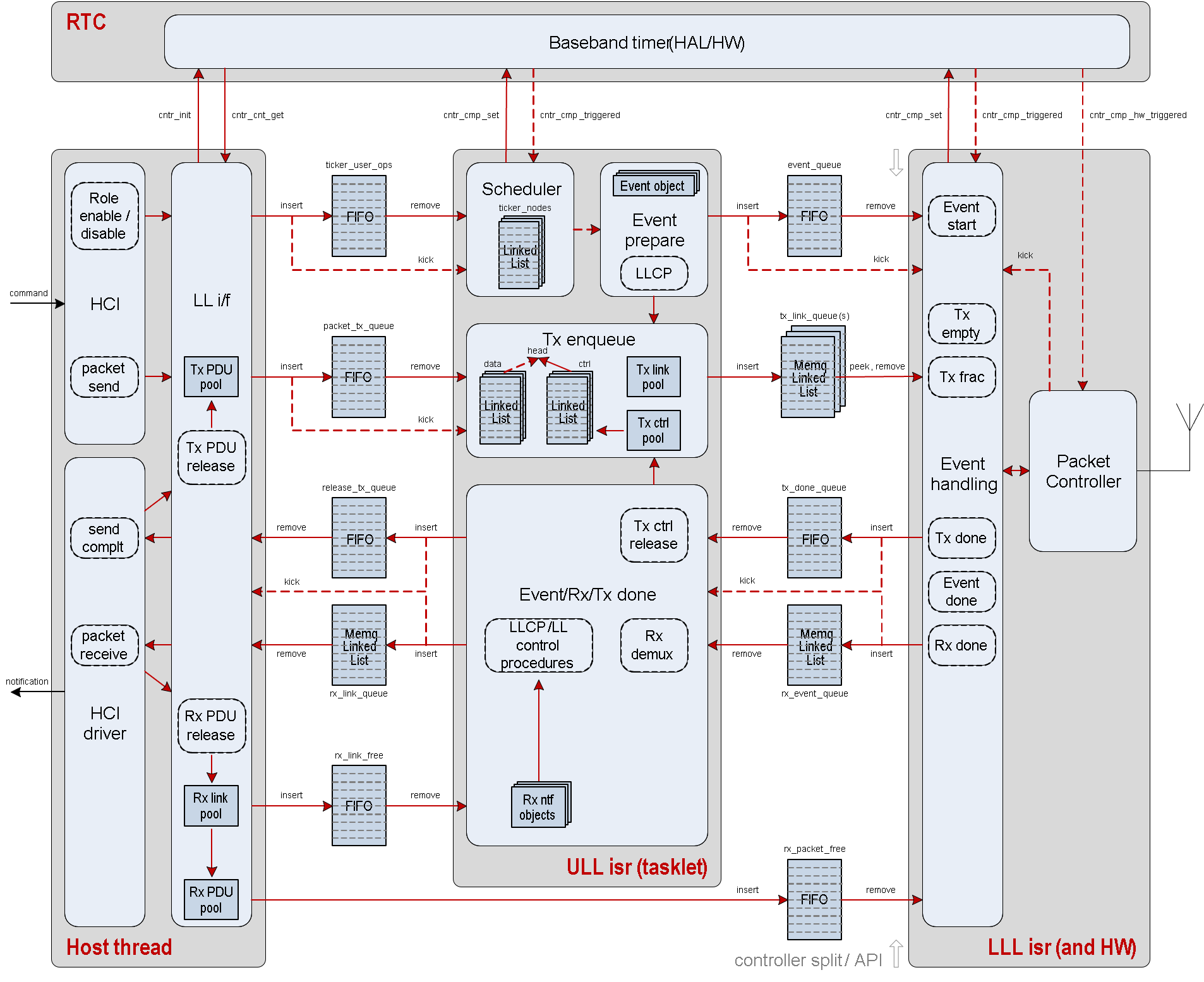

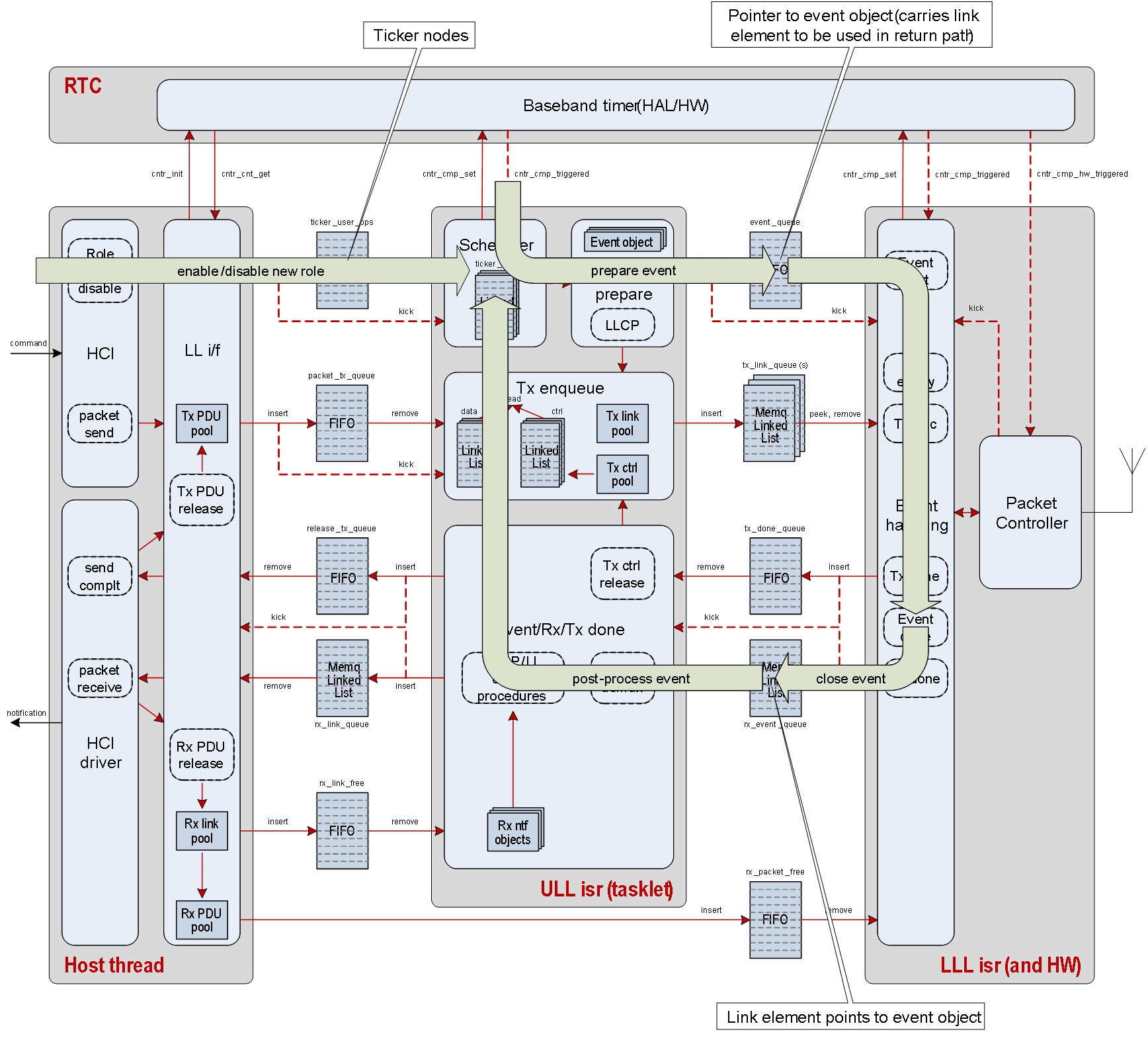

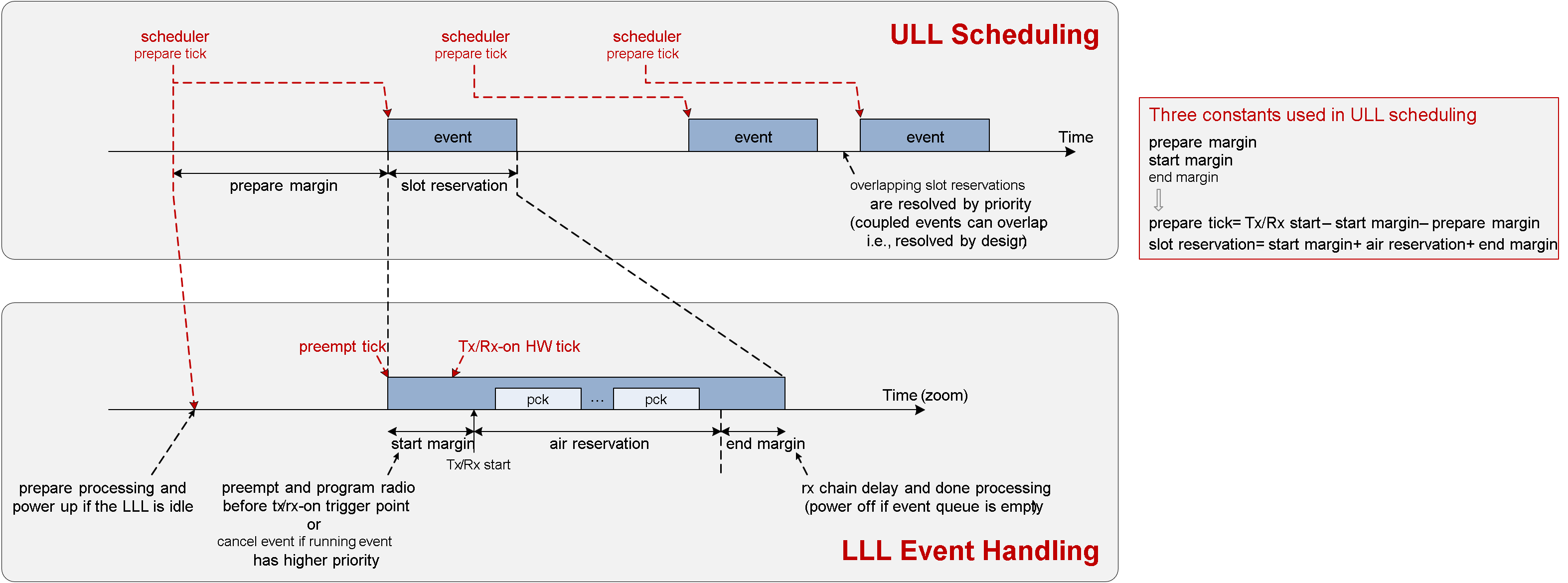

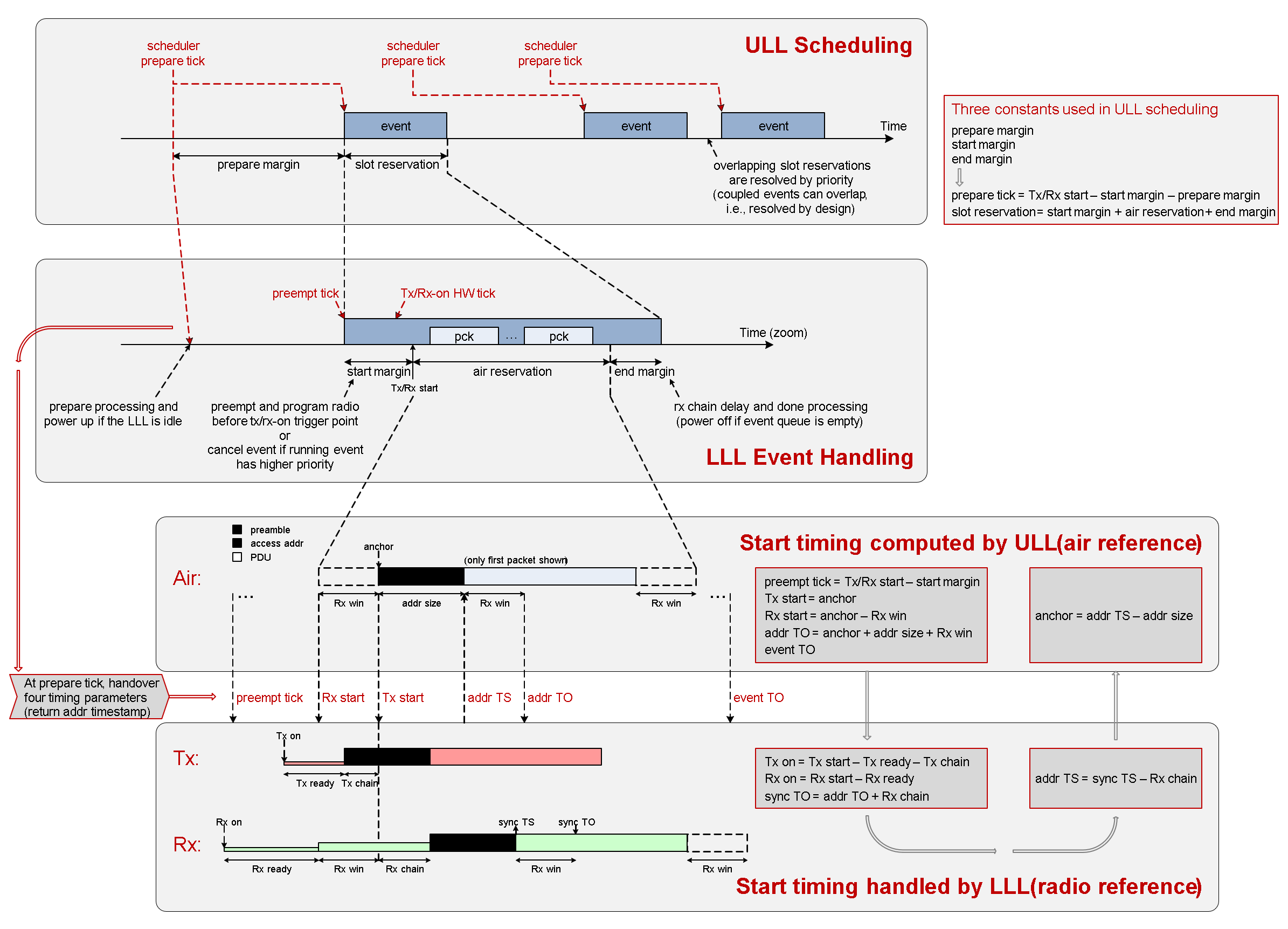

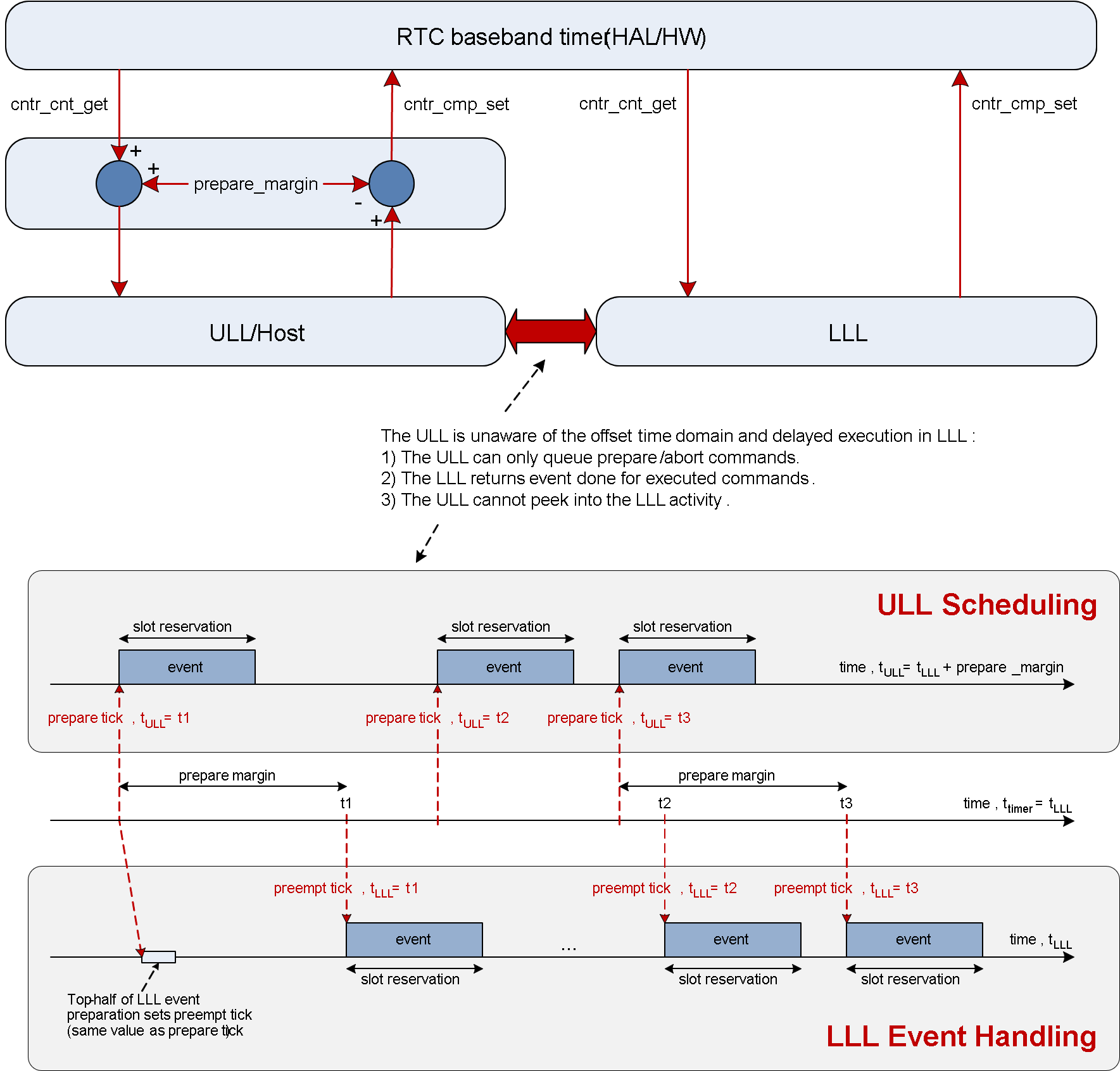

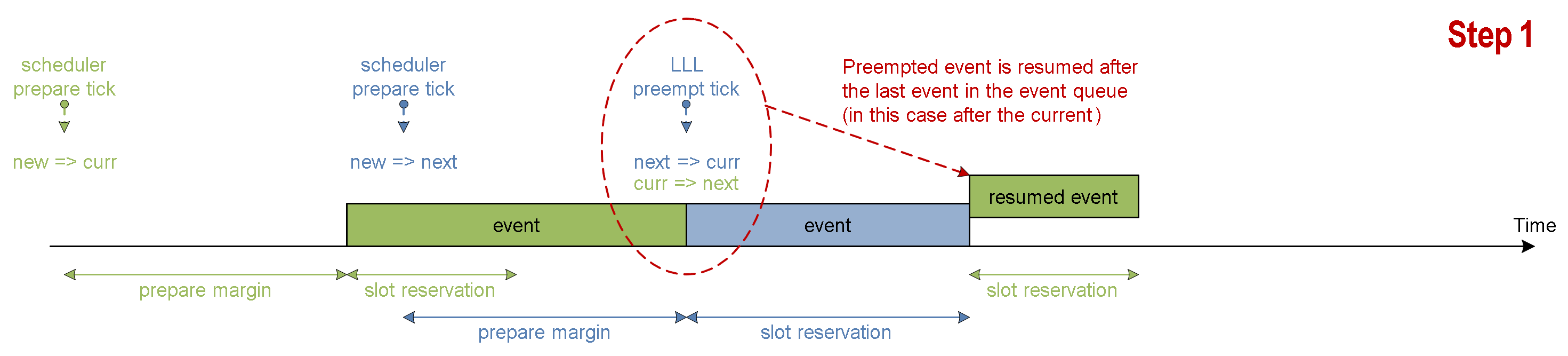

Scheduling

Ticker

Upper Link Layer and Lower Link Layer

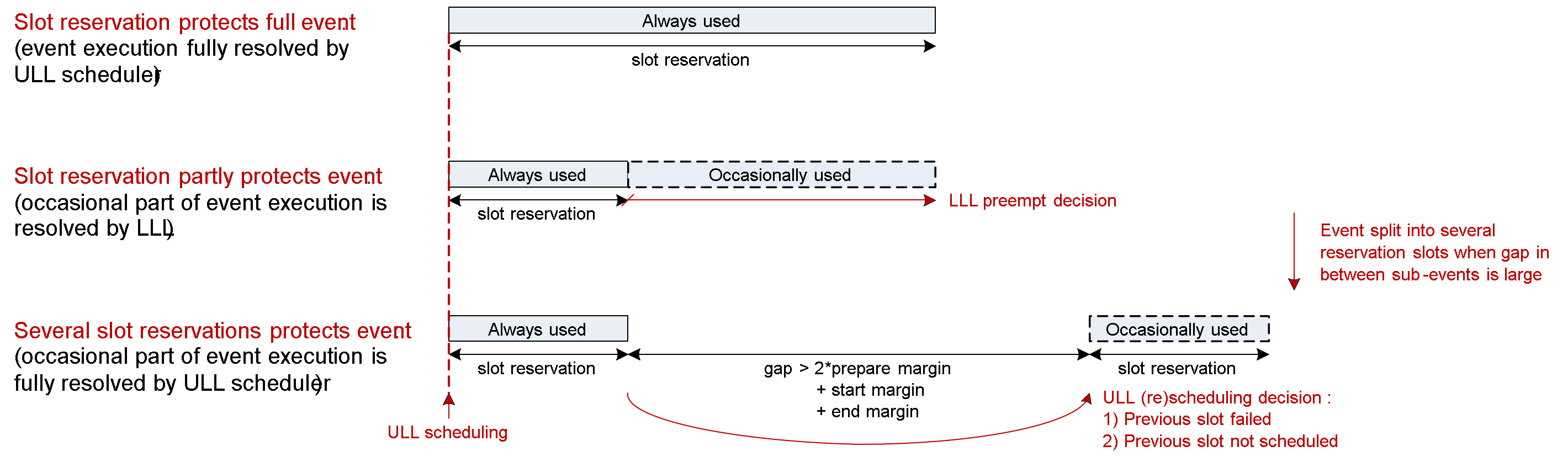

Scheduling Variants

ULL and LLL Timing

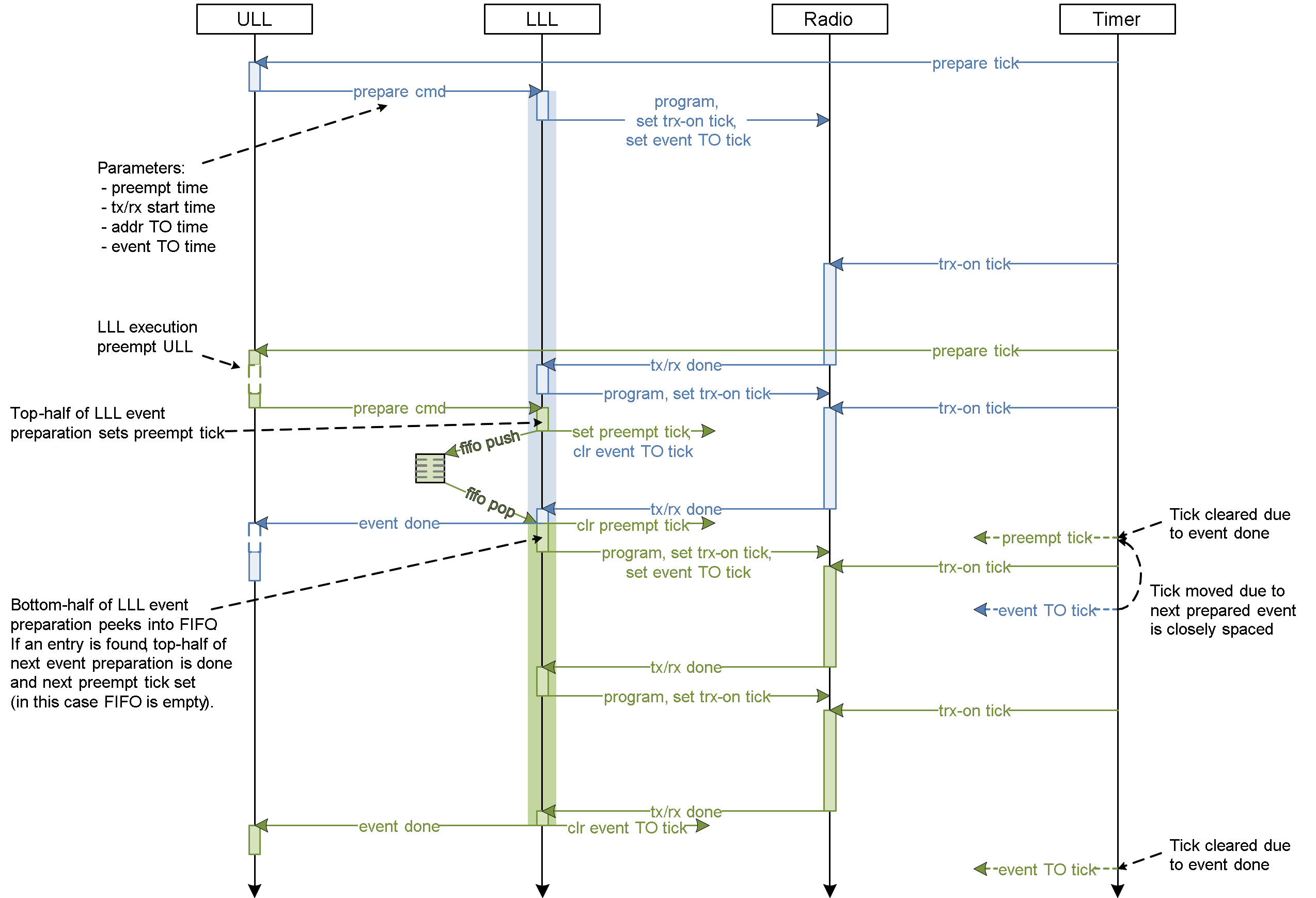

Event Handling

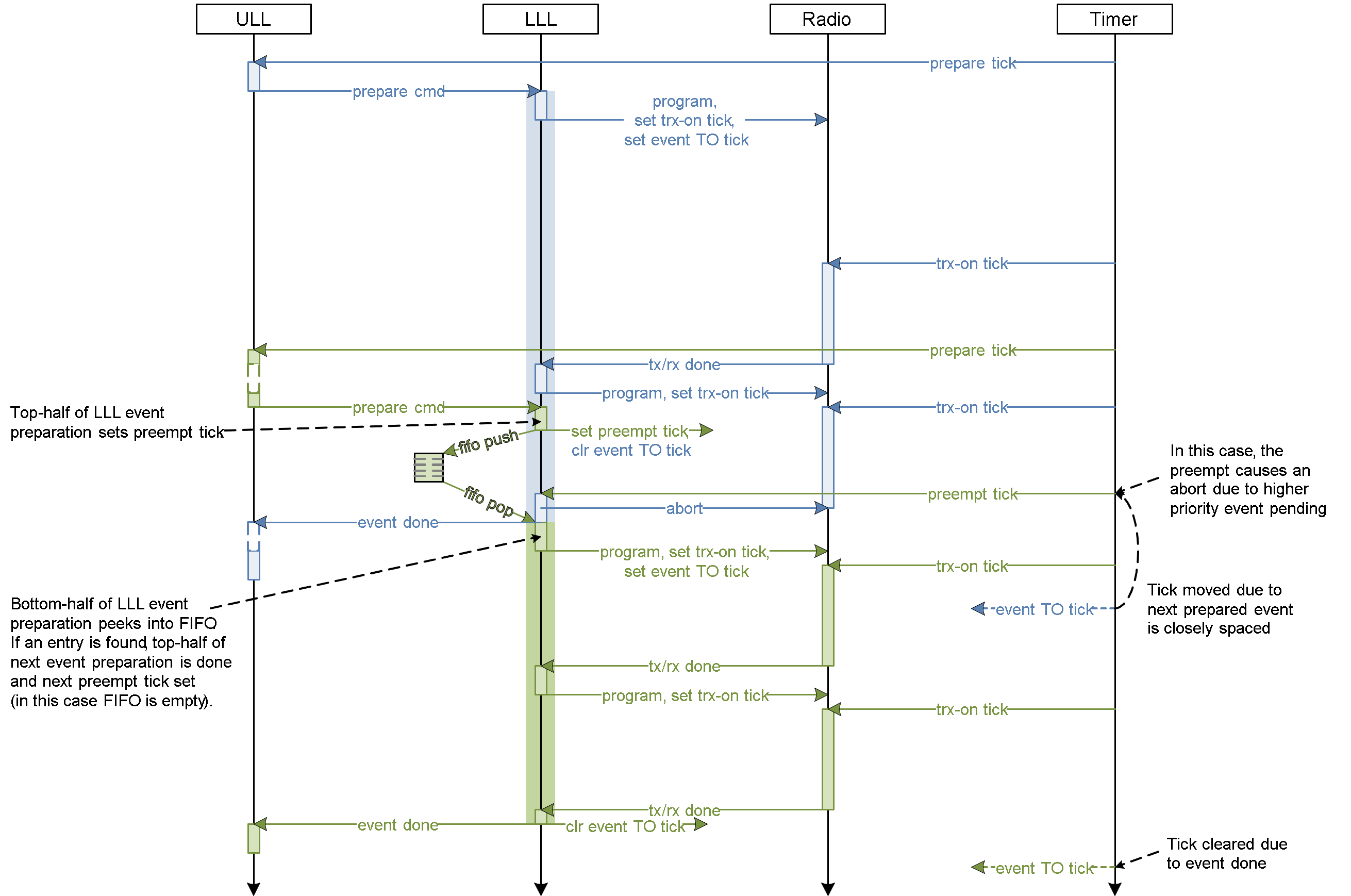

Scheduling Closely Spaced Events

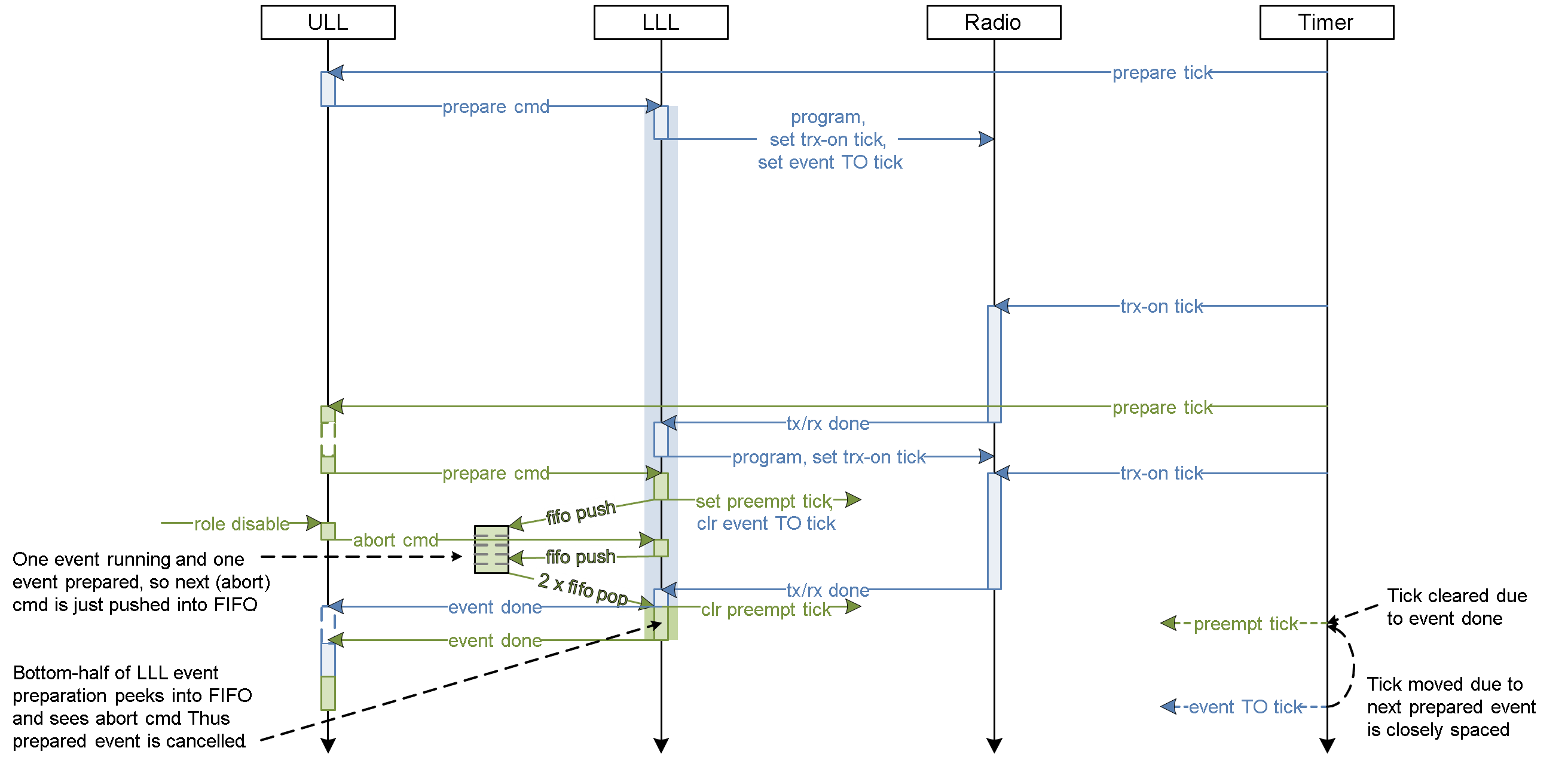

Aborting Active Event

Cancelling Pending Event

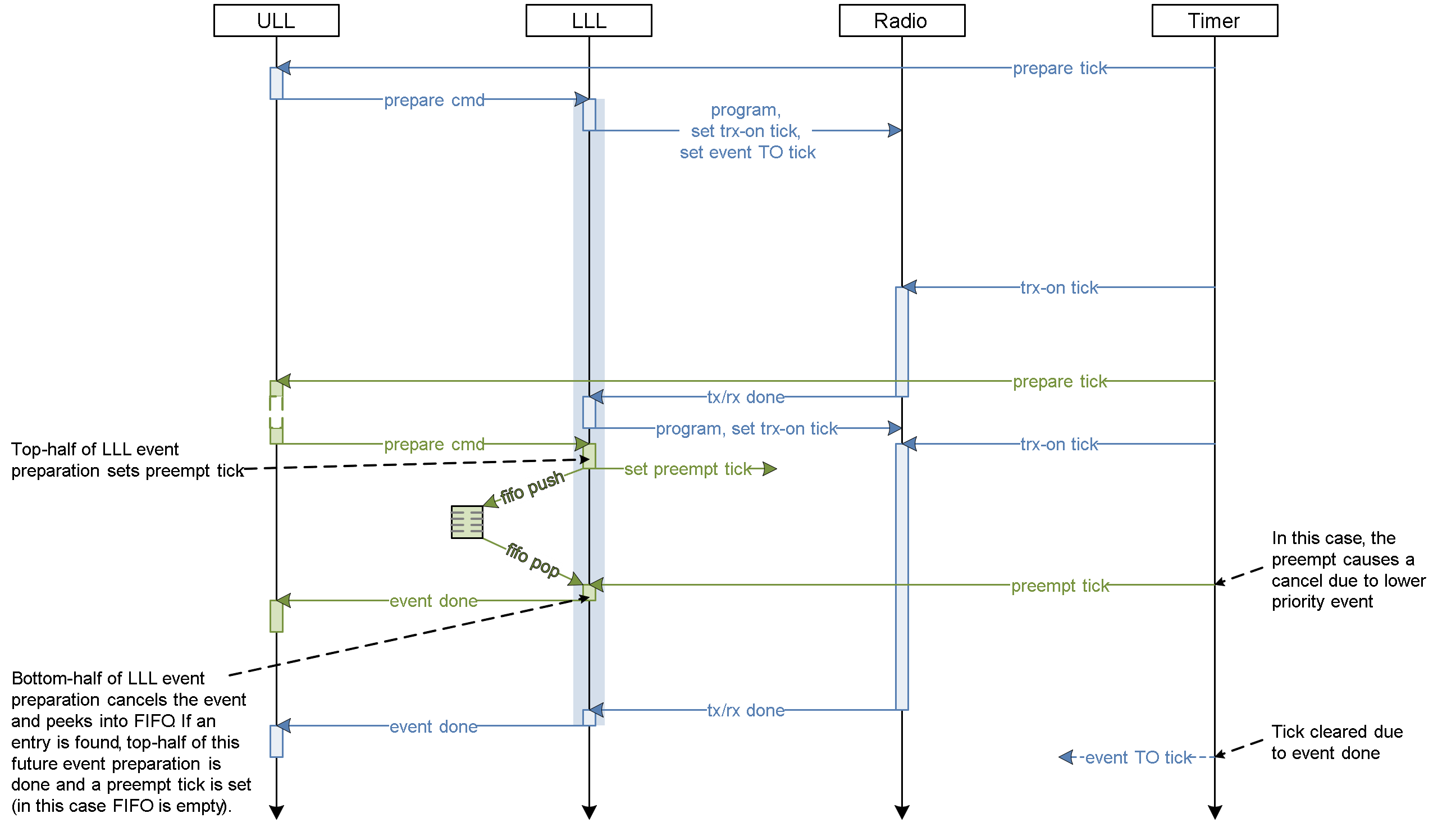

Pre-emption of Active Event

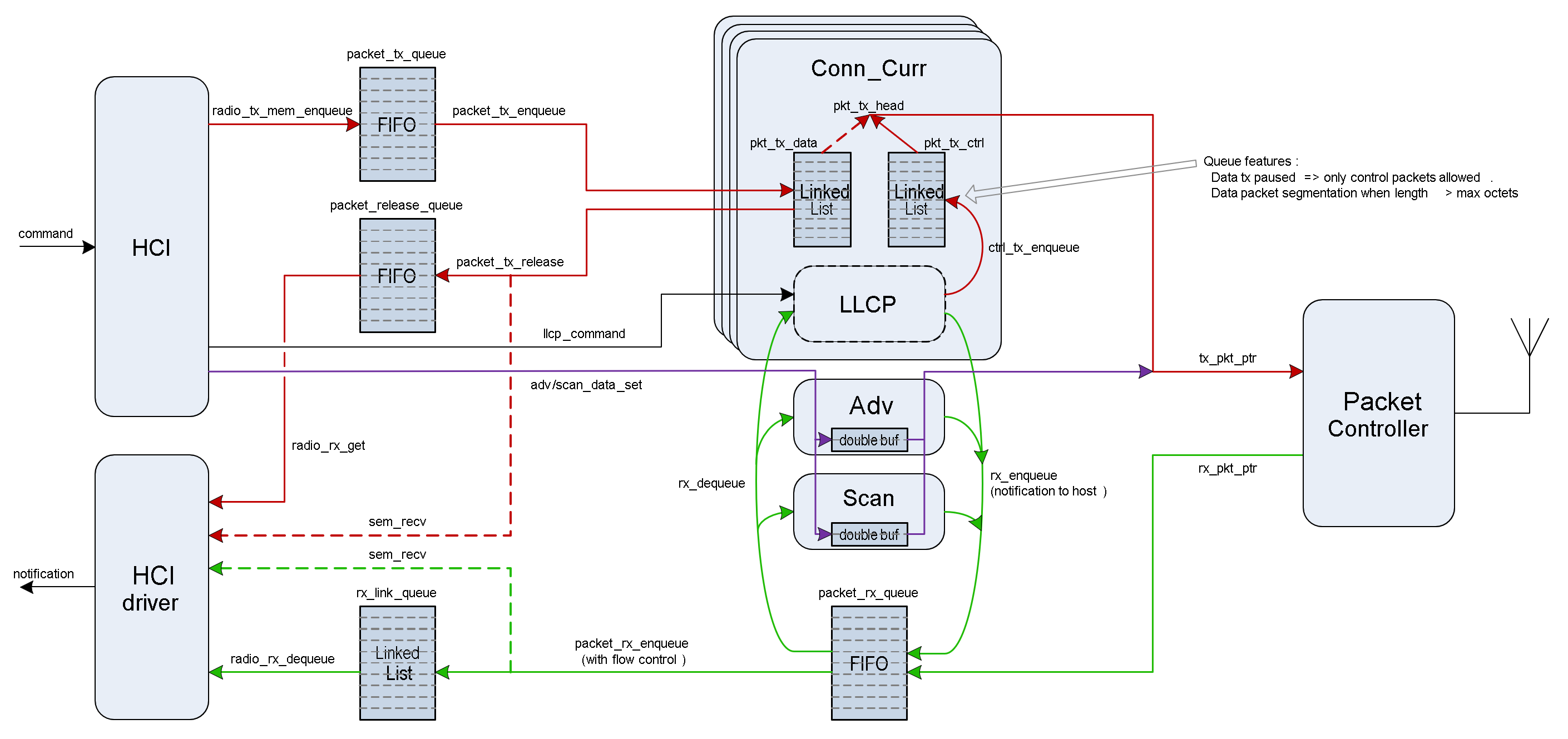

Data Flow

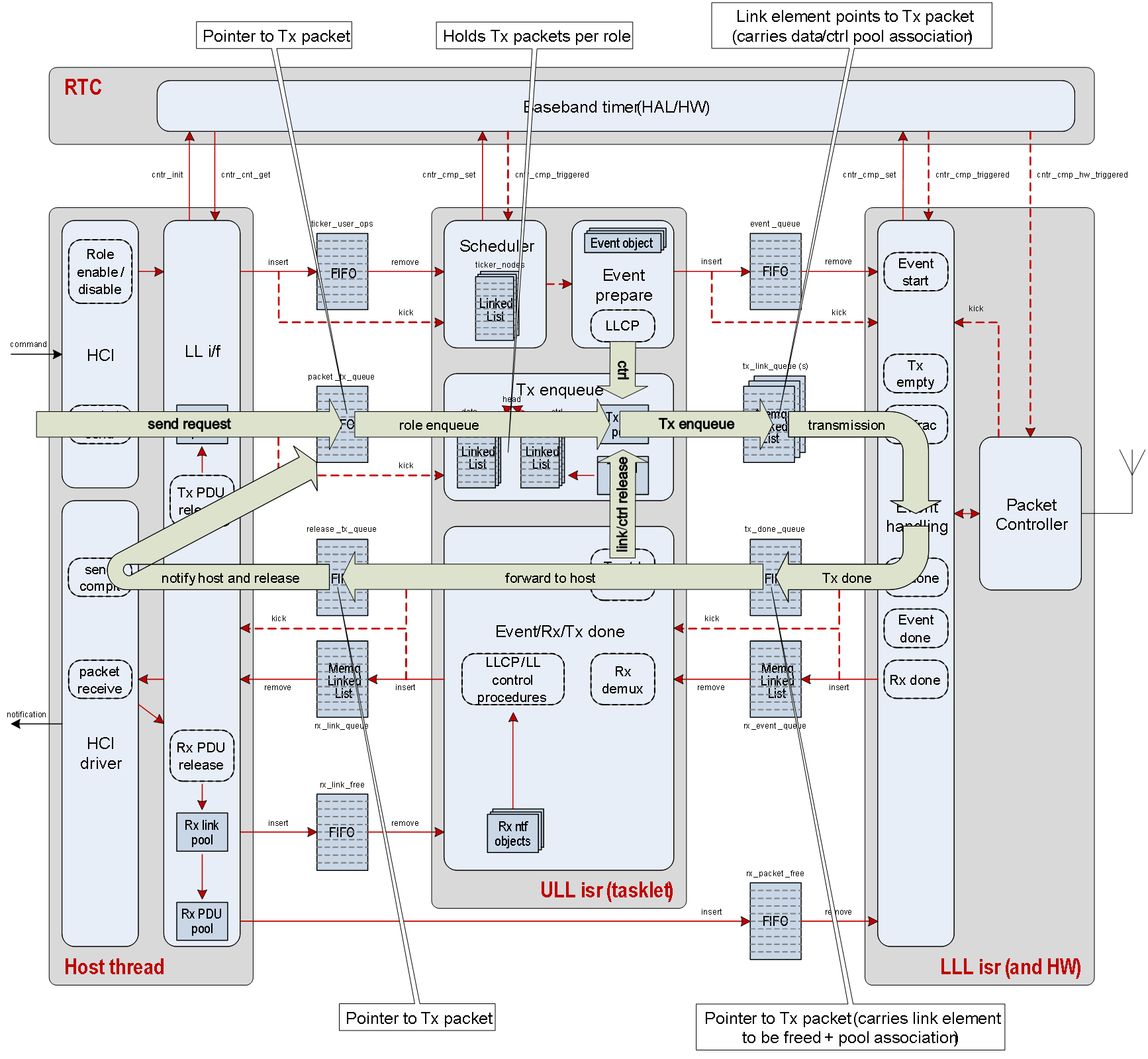

Transmit Data Flow

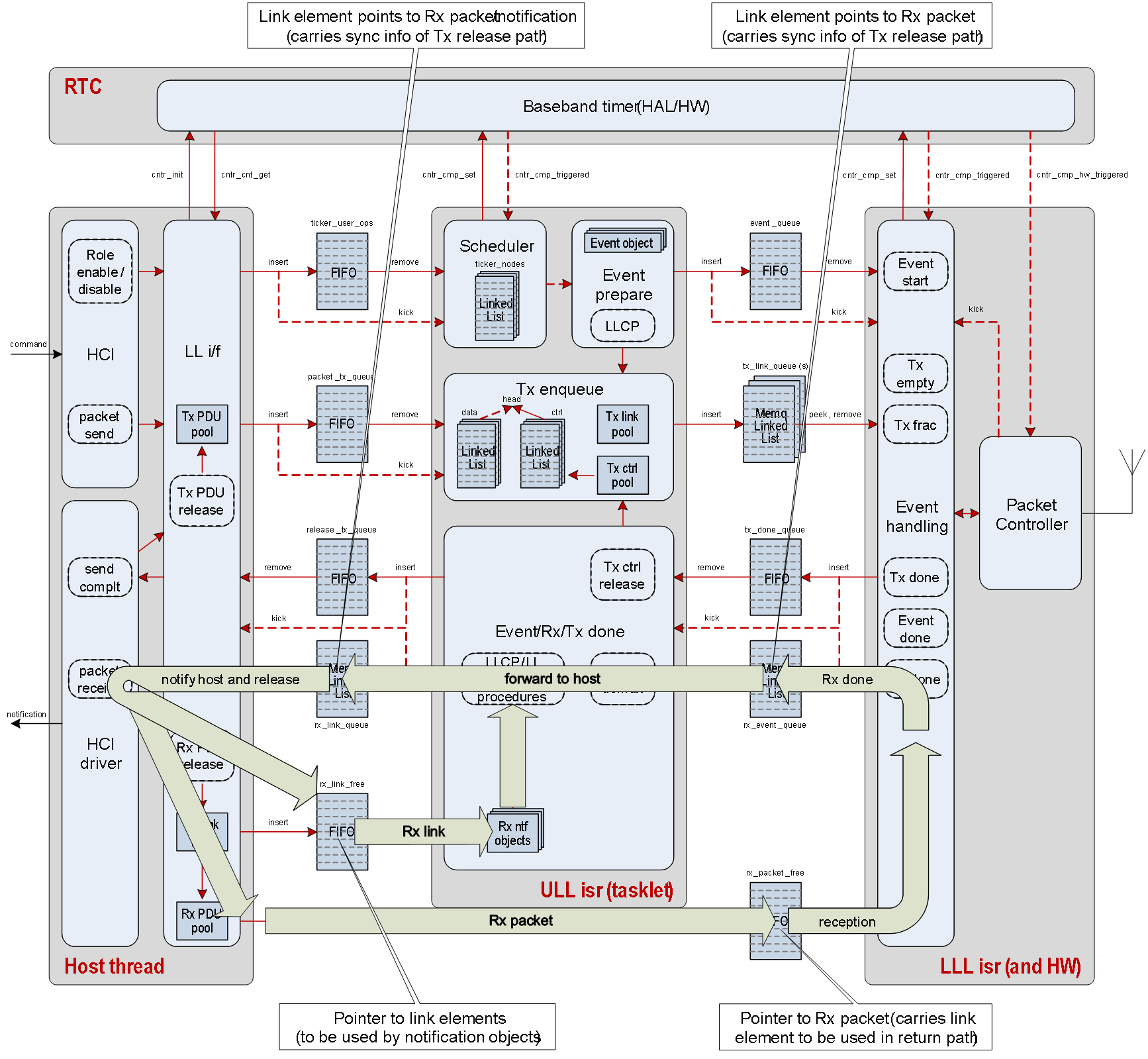

Receive Data Flow

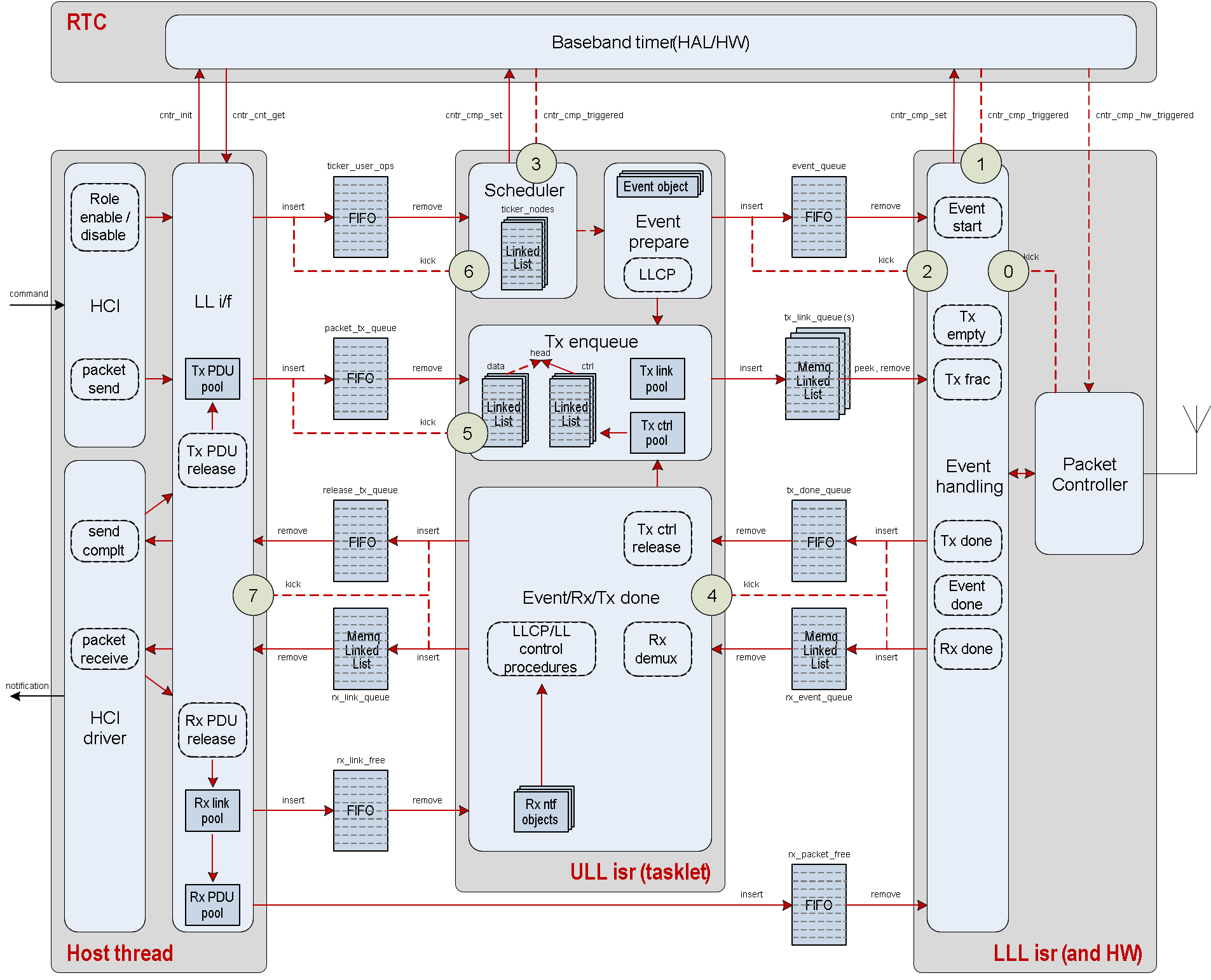

Execution Priorities

Event handle (0, 1) < Event preparation (2, 3) < Event/Rx done (4) < Tx request (5) < Role management (6) < Host (7).

LLL is vendor ISR, ULL is Mayfly ISR concept, Host is kernel thread.

Lower Link Layer

LLL Execution

LLL Resume

Bare metal utilities

Memory FIFO and Memory Queue

Mayfly

Mayfly are multi-instance scalable ISR execution contexts

What a Work is to a Thread, Mayfly is to an ISR

List of functions executing in ISRs

Execution priorities map to IRQ priorities

Facilitate cross execution context scheduling

Race-to-idle execution

Lock-less, bare metal

Legacy Controller

Bluetooth Low Energy Controller - Vendor Specific Details

Hardware Requirements

Nordic Semiconductor

The Nordic Semiconductor Bluetooth Low Energy Controller implementation requires the following hardware peripherals.

Resource |

nRF Peripheral |

# instances |

Zephyr Driver Accessible |

Description |

|---|---|---|---|---|

Clock |

NRF_CLOCK |

1 |

Yes |

|

RTC [a] |

NRF_RTC0 |

1 |

No |

|

Timer |

2 or 1 [1] |

No |

|

|

PPI [b] |

NRF_PPI |

Yes [4] |

|

|

DPPI [c] |

NRF_DPPI |

20 channels, and 2 channel groups [3] |

Yes [4] |

|

SWI [d] |

NRF_SWI4 and NRF_SWI5, or NRF_SWI2 and NRF_SWI3 [5] |

2 |

No |

|

Radio |

NRF_RADIO |

1 |

No |

|

RNG [e] |

NRF_RNG |

1 |

Yes |

|

ECB [f] |

NRF_ECB |

1 |

No |

|

CBC-CCM [g] |

NRF_CCM |

1 |

No |

|

AAR [h] |

NRF_AAR |

1 |

No |

|

GPIO [i] |

NRF_GPIO |

2 GPIO pins for PA and LNA, 1 each |

Yes |

|

GPIOTE [j] |

NRF_GPIOTE |

1 |

Yes |

|

TEMP [k] |

NRF_TEMP |

1 |

Yes |

|

UART [l] |

NRF_UART0 |

1 |

Yes |

|

IPC [m] |

NRF_IPC [5] |

1 |

Yes |

|

Real Time Counter (RTC)

Programmable Peripheral Interconnect (PPI)

Distributed Programmable Peripheral Interconnect (DPPI)

Software Interrupt (SWI)

Random Number Generator (RNG)

AES Electronic Codebook Mode Encryption (ECB)

Cipher Block Chaining (CBC) - Message Authentication Code with Counter Mode encryption (CCM)

Accelerated Address Resolver (AAR)

General Purpose Input Output (GPIO)

GPIO tasks and events (GPIOTE)

Temperature sensor (TEMP)

Universal Asynchronous Receiver Transmitter (UART)

Interprocess Communication peripheral (IPC)